# DIGITAL ELECTRONICS VOLUME 2

Z

# FLIP FLOP

NORAZITA BINTI IBRAHIM PUTERI NADIA DAYANIE BINTI MEGAT SABRI

# FLIP-FLOP DIGITAL ELECTRONICS VOLUME 2

By: NORAZITA BINTI IBRAHIM PUTERI NADIA DAYANIE BINTI MEGAT SABRI

> Politeknik Ungku Omar 2024

## FLIP-FLOP DIGITAL ELECTRONICS VOLUME 2

First Issue 2024 eISBN

e ISBN 978-629-7635-63-7

#### All rights reserved

It is not permitted to reproduced any part of the writing of this ebook in any form and any means whatsoever whether electronically, photocopying, mechanically, recording or in any way except with the permission of the author.

The author also does not guarantee that what is contained is suitable for the reader but all content is through the author's own experience and expertise

Published by: Politeknik Ungku Omar Jalan Raja Musa Mahadi 31400 Ipoh Perak

Email: razita@puo.edu.my ndayanie@puo.edu.my

# **AUTHOR BIODATA**

## NORAZITA BINTI IBRAHIM

is a lecturer in Electrical Engineering Department, Ungku Omar Polytechnic. She has a Bachelor of Engineering (Electrical) and has been lecturing Electrical Engineering courses for 21 years

## PUTERI NADIA DAYANIE BINTI MEGAT SABRI

is a lecturer in Electrical Engineering Department, Ungku Omar Polytechnic. She has a Master Electronic Engineering (Electronic System) and has been lecturing Electrical Engineering courses for 13 years

## **ACKNOWLEDGEMENTS**

Bismillahirrahmanirrohim In the name of Allah, the Most Gracious and the Most Merciful.

Alhamdulillah, first and foremost, we want to praises and thanks to Allah for completing our second e-book successfully. Without his will we would not be able to complete this e-book.

Secondly, special thanks to Polytechnic Ungku Omar especially Electrical Engineering Department, for providing us with the inspiration and opportunity to create this e-book.

We would like to extend my deepest gratitude to our family for their unwavering support and encouragement throughout this journey.

We hope that this e-book will be beneficial, especially to students, and provide valuable insights and knowledge that can aid in their studies.

Thank you all for your support and contributions, which have made this e-book possible.

## **PREFACE**

This book, Digital Electronics Volume 2, focuses on Chapter 3, which covers Flip–Flops. The chapter introduces the fundamental concepts of Flip–Flops, offering a clear understanding of their circuits, truth tables, and timing diagrams. Designed to aid students in mastering these essential topics, this e-book includes concise explanations, practical examples, and exercises for each subtopic. These resources are intended to reinforce learning and deepen comprehension of Flip–Flop circuits and their applications.

## **CONTENTS**

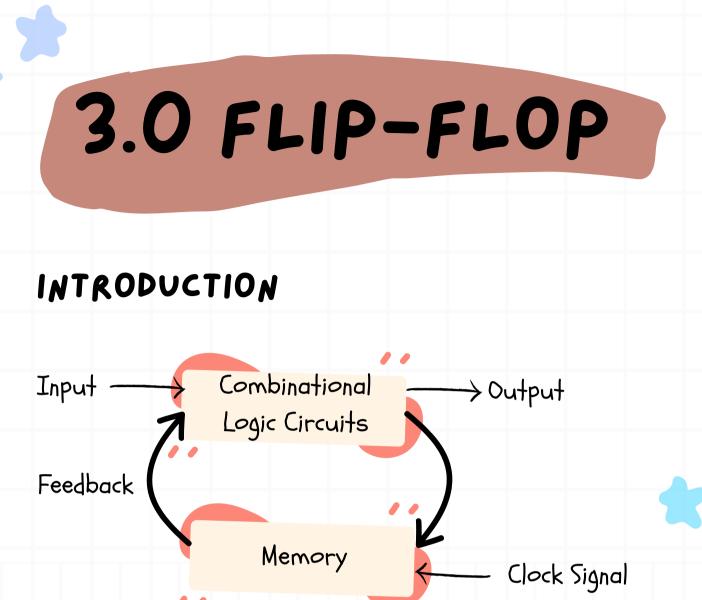

#### **Combinational Logic Circuits**

- No memory

- Change state depending upon the actual signals being applied to their inputs

#### **Sequential Logic Circuits**

- Have some form of inherent "Memory"

- Each of inputs and outputs can either of 2 stages:

- Logic 0

- Logic 1

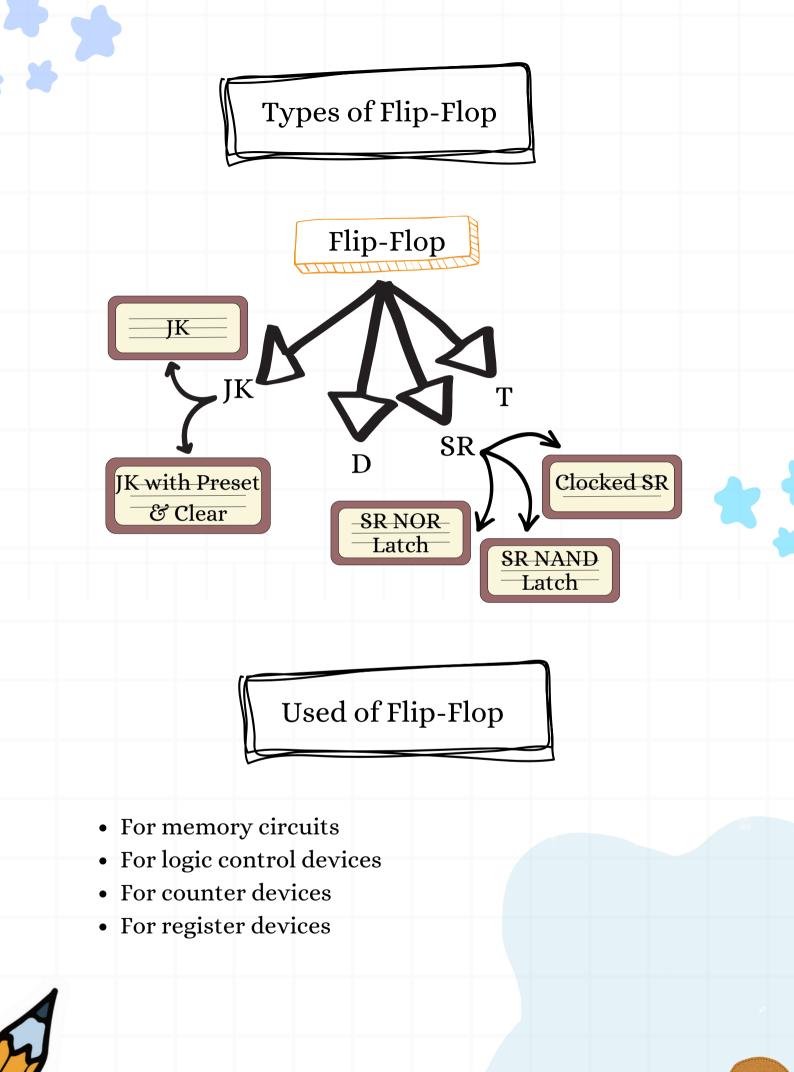

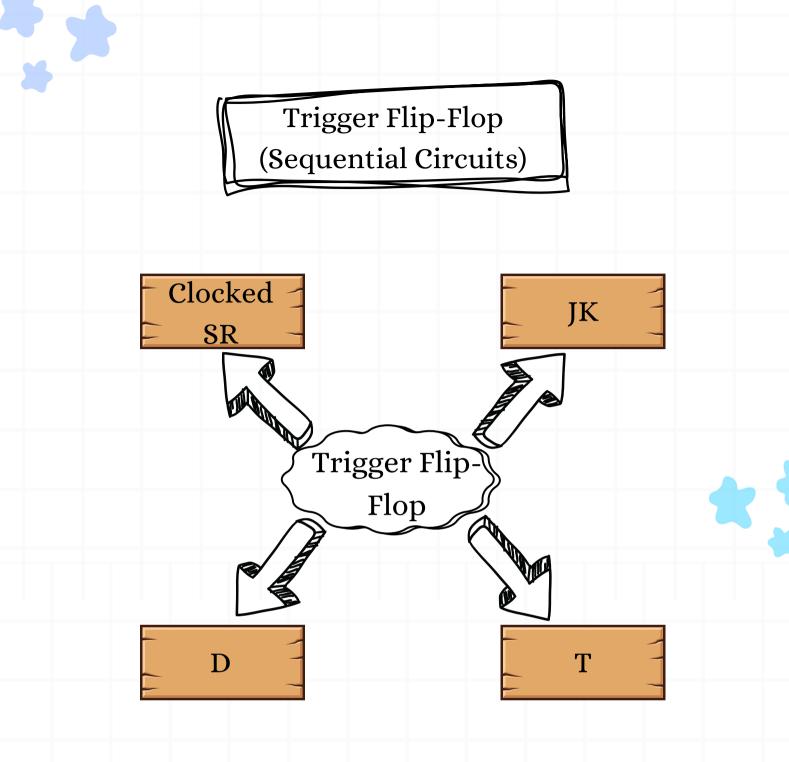

## 3.1 REMEMBER TYPES OF FLIP-FLOPS

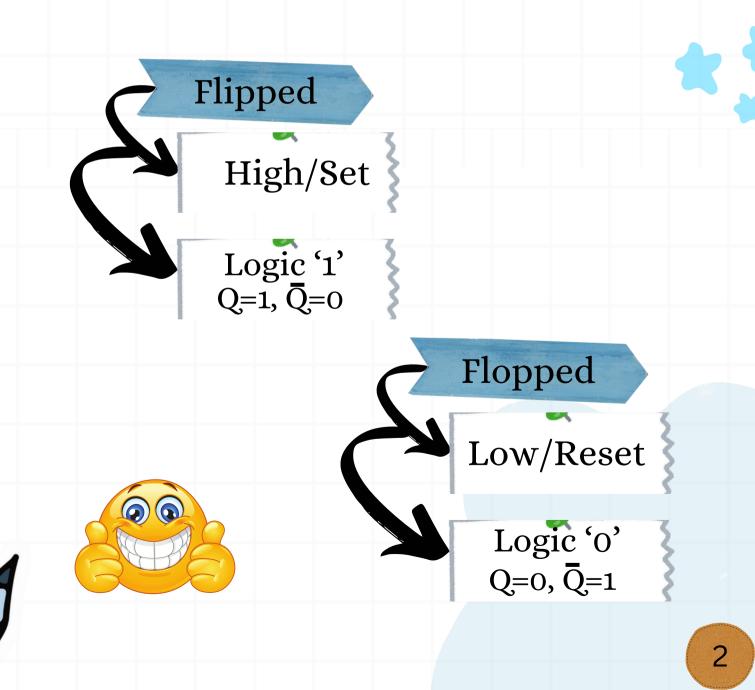

Flip-flop is a kind of bistable multivibrator. It is a Sequential Circuit which has two stable states and is capable of serving as one bit of memory, bit 1 or bit 0.

- Have two stable conditions.

- Can be switched from one to the other by appropriate inputs.

- Stable conditions usually called the **states**.

- (1=High, 0=Low)

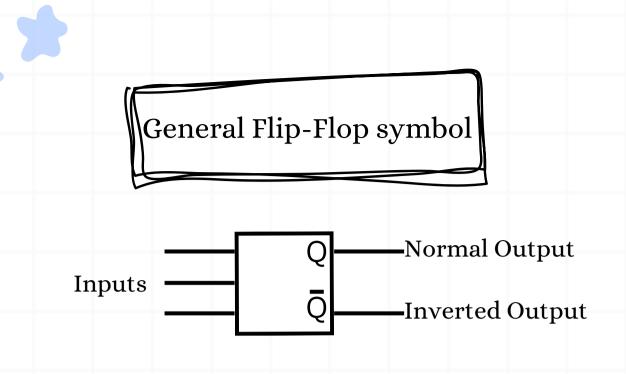

- Q is normal output.

- More complicated Flip-Flop use a clock as the control input.

## 3.2 UNDERSTAND OPERATION OF EACH TYPE OF FLIP-FLOP

- Basic flip-flop and is an asynchronous counter.

- The outputs is immediately change anytime one or more of the inputs change just as in combinational logic circuit.

- Does not operate in step with a clock or timing.

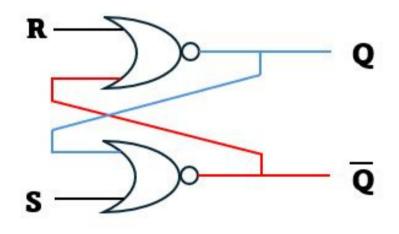

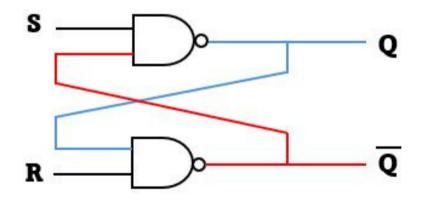

- Can be constructed using two NAND gates latch or two NOR gates latch.

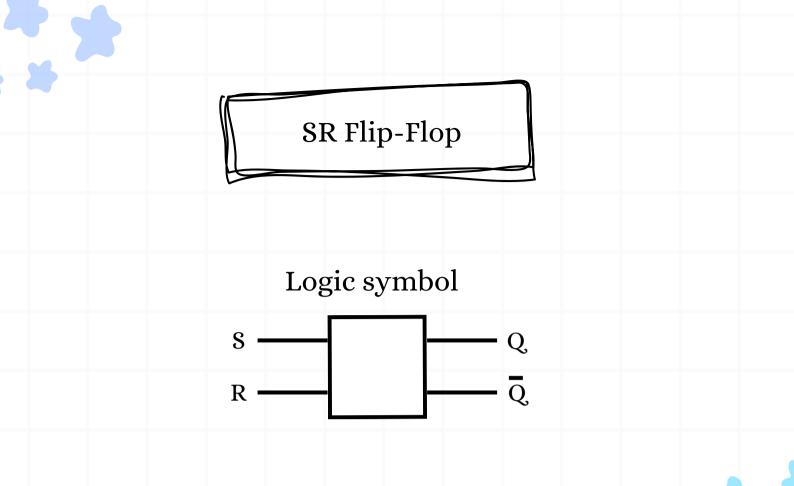

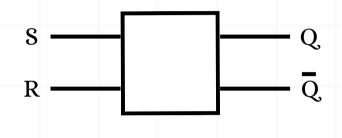

- Has two inputs, SET (S) and RESET (R).

- Has two outputs, Q and  $\overline{\mathbf{Q}}$ .

- Q is the normal output and is the one most used.

- $\overline{\mathbf{Q}}$  is simply the compliment of output  $\mathbf{Q}$ .

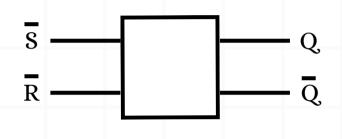

Logic symbol / Block Diagram

Logic Circuit

#### Truth Table

| MODE OF      | OUTPUT |   | INPUT |   |

|--------------|--------|---|-------|---|

| OPERATION    | Q      | Q | R     | s |

| HOLD (H)     | Q      | Q | 0     | 0 |

| RESET (R)    | 1      | 0 | 1     | 0 |

| SET (S)      | 0      | 1 | 0     | 1 |

| INVALID (INV | 0      | 0 | 1     | 1 |

#### 1.Complete the truth table for SR NOR Latch below.

| Input |   | Output |   | Mode of   |

|-------|---|--------|---|-----------|

| S     | R | Q      | Q | Operation |

| 1     | 0 |        |   |           |

| 0     | 0 | 2<br>2 |   | 5<br>1    |

| 0     | 1 |        |   |           |

| 0     | 0 |        |   | 8         |

| 1     | 1 |        |   |           |

| 1     | 0 |        |   | 8         |

| 0     | 1 |        |   |           |

| 0     | 0 |        |   | A.        |

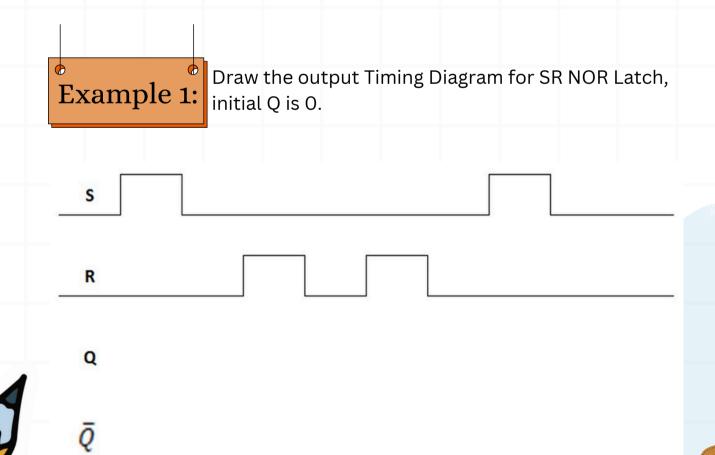

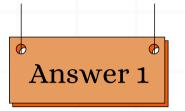

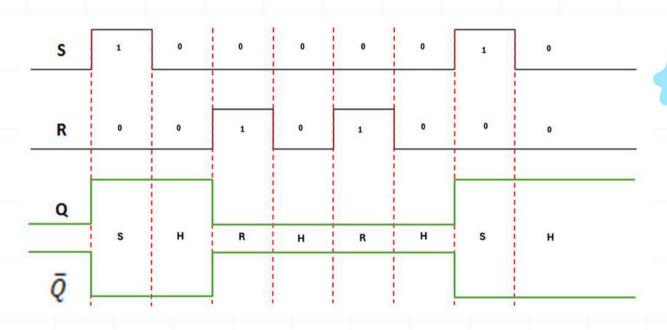

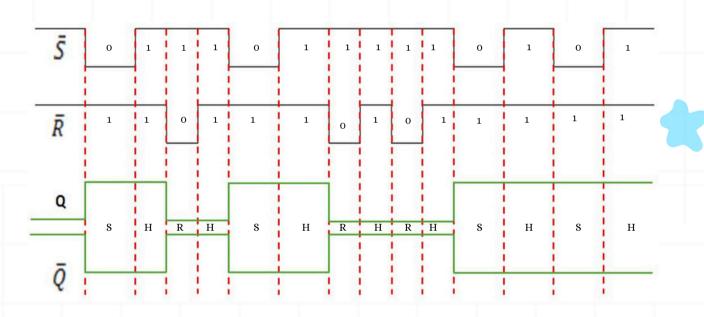

2.Draw the output Timing Diagram for SR NOR Latch, initial Q is 0.

10

Logic symbol / Block Diagram

Logic Circuit

### Truth Table

| INP | INPUT |   | PUT | MODE OF       |

|-----|-------|---|-----|---------------|

| S   | R     | Q | Q   | OPERATION     |

| 0   | 0     | 1 | 1   | INVALID (INV) |

| 0   | 1     | 1 | 0   | SET (S)       |

| 1   | 0     | 0 | 1   | RESET (R)     |

| 1   | 1     | Q | Q   | HOLD (H)      |

#### 1.Complete the truth table for SR NAND Latch below.

| Input |   | Out | tput | Mode of   |

|-------|---|-----|------|-----------|

| S     | R | Q   | Q    | Operation |

| 0     | 1 |     |      |           |

| 1     | 0 |     |      |           |

| 0     | 1 |     |      |           |

| 1     | 1 |     |      |           |

| 0     | 0 |     |      |           |

| 1     | 0 |     |      |           |

| 0     | 1 |     |      |           |

| 1     | 1 |     |      |           |

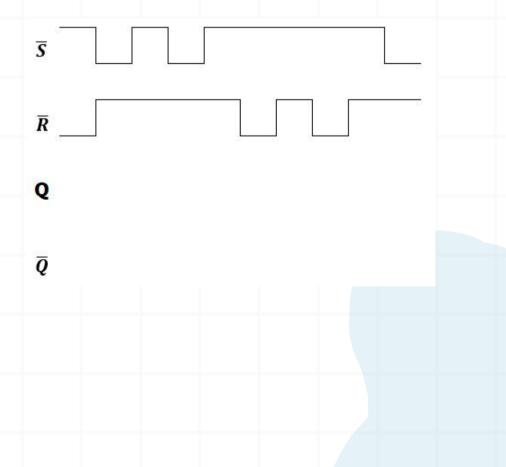

#### 2.Draw the output Timing Diagram for SR NOR Latch, initial Q is 0.

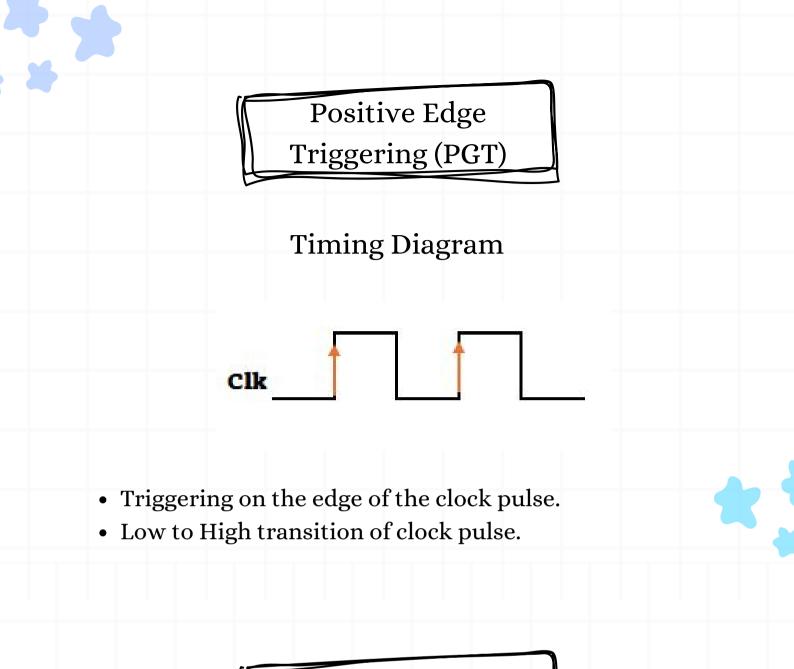

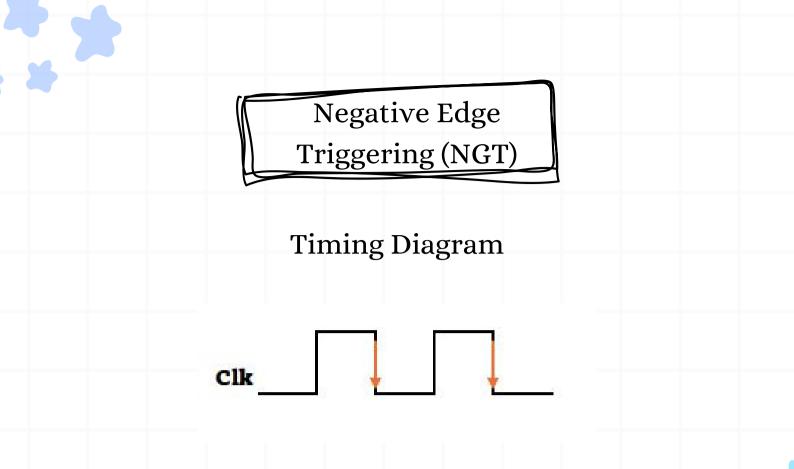

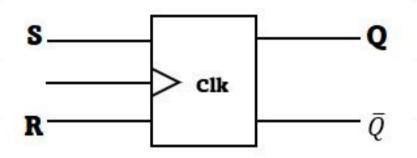

- Depends on clock pulse applied to their inputs.

- The result of flip-flop responding to a clock input is called clock-pulse-triggering.

- 2 types: a) Positive Edge Triggering (PGT)

b) Negative Edge Triggering (NGT)

## The Clock

- The exact times at which any output can change states are controlled by a signal.

- Clock signal is generally a rectangular pulse train or a square wave.

- Clock is distributed to all parts of the system, and most of the system outputs can change state only when the clock makes a transition.

- PGT clock changes from a LOW state to a HIGH state.

- NGT clock changes from a HIGH state to a LOW state.

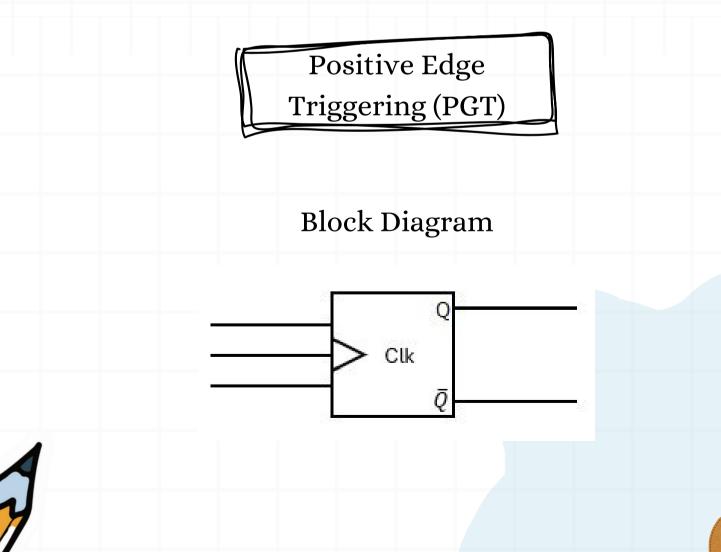

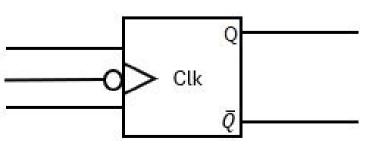

Block Diagram

- Triggering on the edge of the clock pulse.

- High to Low transition of clock pulse.

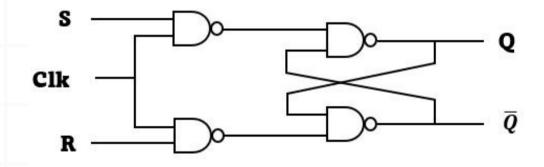

Logic symbol / Block Diagram

Logic Circuit

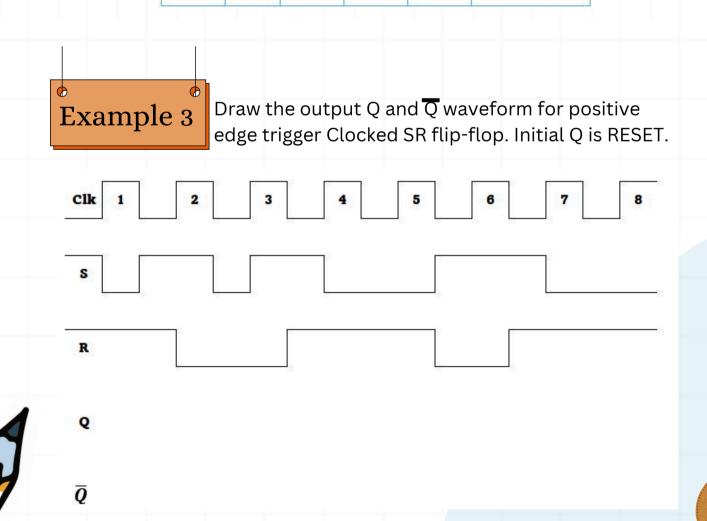

### Truth Table

| MODE OF       | OUTPUT |   | INPUT |   |     |

|---------------|--------|---|-------|---|-----|

| OPERATION     | Q      | Q | R     | S | CLK |

| HOLD (H)      | Q      | Q | 0     | 0 | 1   |

| RESET (R)     | 1      | 0 | 1     | 0 | 1   |

| SET (S)       | 0      | 1 | 0     | 1 | 1   |

| INVALID (INV) | 1      | 1 | 1     | 1 | 1   |

| HOLD (H)      | Q      | Q | x     | x | 0   |

20

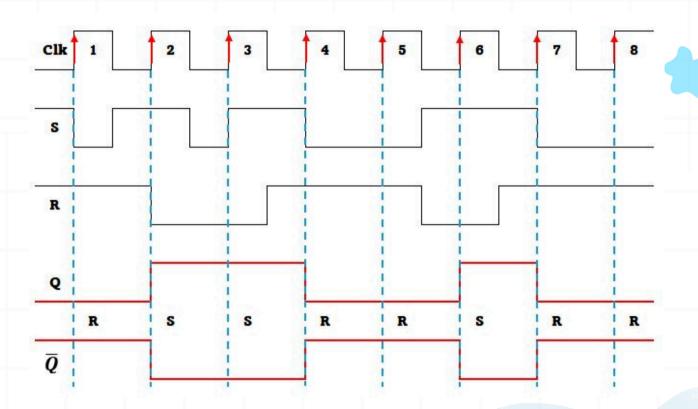

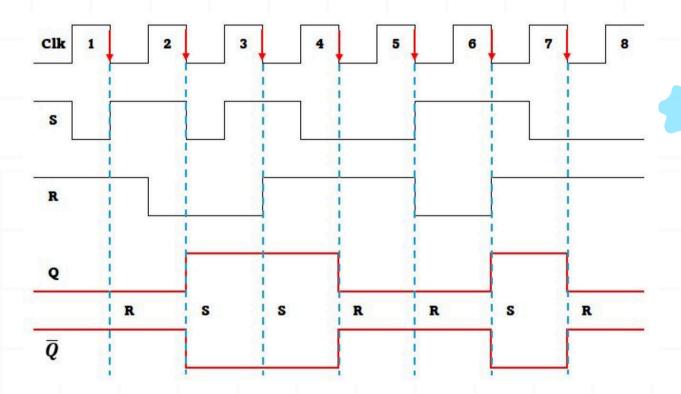

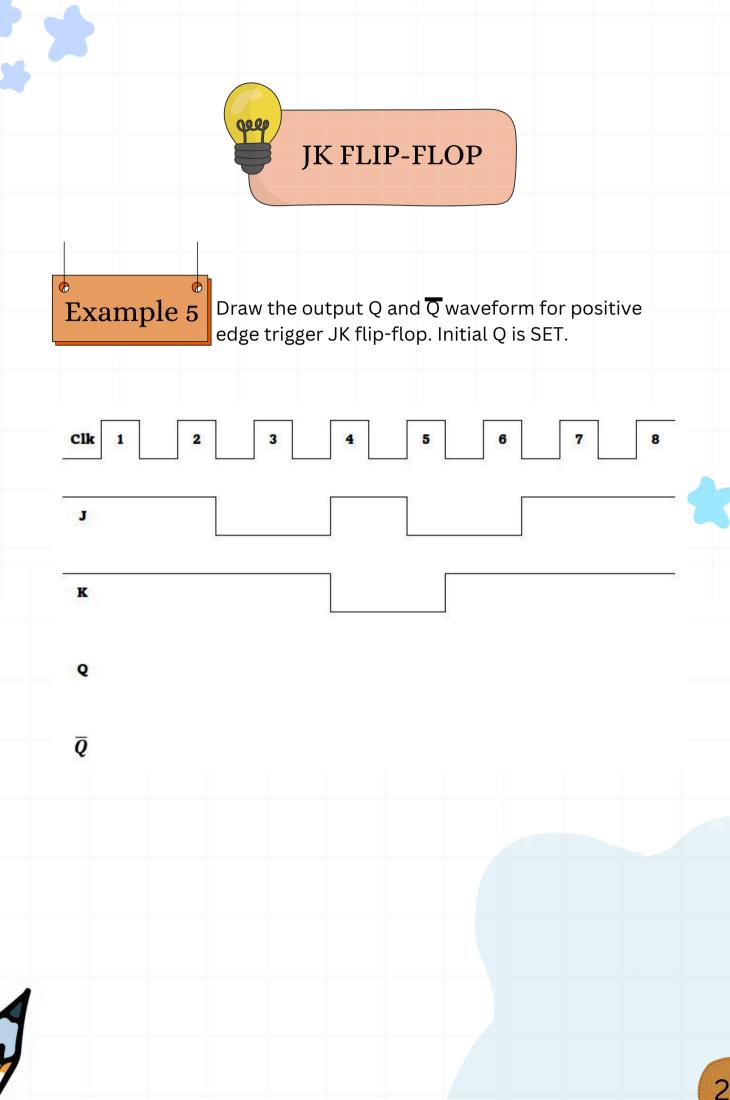

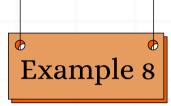

Draw the output Q and  $\overline{Q}$  waveform for negative Example 4 edge trigger Clocked SR flip-flop. Initial Q is RESET.

Q

0

$\overline{Q}$

1.Complete the truth table for CLOCKED SR flip-flop below.

| Input |   | Output |   | Mode of |           |  |

|-------|---|--------|---|---------|-----------|--|

| Clock | s | R      | Q | Q       | Operation |  |

| 1     | 1 | 0      |   |         |           |  |

| 0     | 0 | 1      |   |         |           |  |

| 1     | 0 | 1      |   |         |           |  |

| 1     | 0 | 0      |   |         |           |  |

| 0     | 1 | 1      |   |         |           |  |

| 1     | 1 | 1      |   |         |           |  |

| 1     | 1 | 0      |   |         |           |  |

| 0     | 0 | 1      |   |         |           |  |

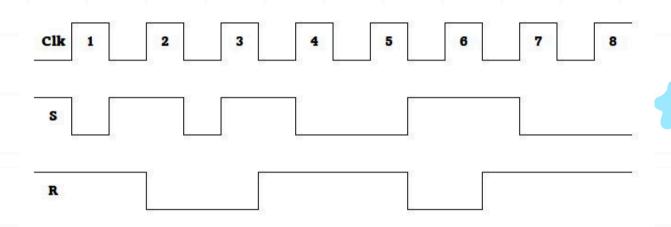

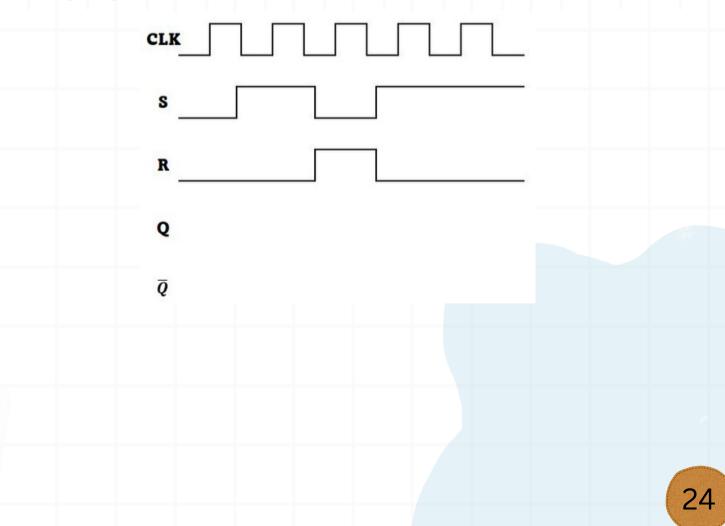

2.Draw the output Q and  $\overline{Q}$  waveform for positive edge trigger Clocked SR flip-flop. Initial Q is RESET.

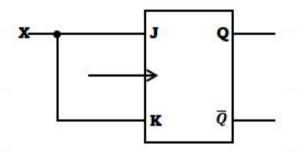

- Versatile and widely used type of flip-flop.

- Functioning of JK is same of the SR in the SET, RESET and HOLD conditions of operation.

- The difference is, the JK flip-flop has no INVALID state as does the SR flip-flop.

- When J and K inputs are HIGH (1), output is TOGGLE (change condition) mode.

- JK flip-flop connected for TOGGLE operation is sometimes called a T flip-flop.

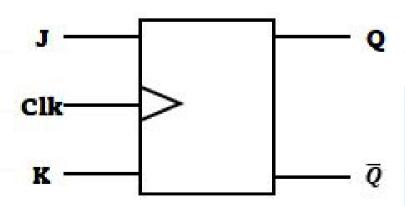

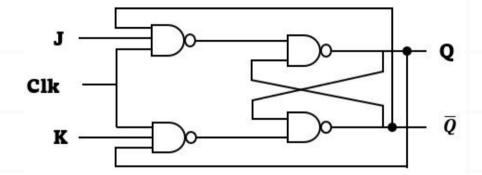

Logic symbol / Block Diagram

## Logic Circuit

### Truth Table

| INPUT |   |   | OUTPUT |   | MODE OF    |  |

|-------|---|---|--------|---|------------|--|

| CLK   | L | к | Q      | Q | OPERATION  |  |

| 1     | 0 | 0 | Q      | Q | HOLD (H)   |  |

| 1     | 0 | 1 | 0      | 1 | RESET (R)  |  |

| 1     | 1 | 0 | 1      | 0 | SET (S)    |  |

| 1     | 1 | 1 | Q      | Q | TOGGLE (T) |  |

| 0     | x | х | Q      | Q | HOLD (H)   |  |

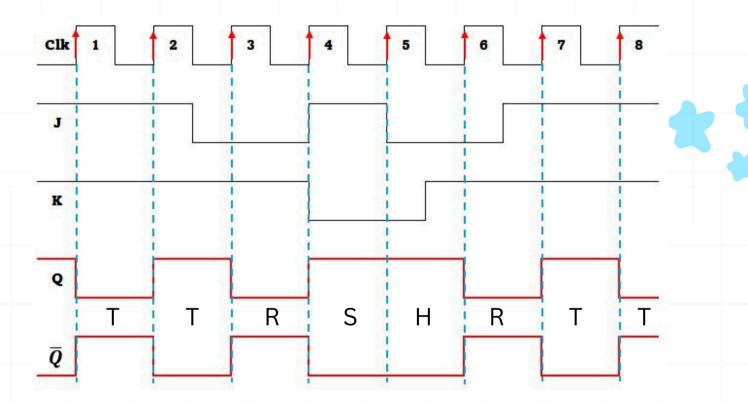

1. Complete the table below for the output and mode of operation for JK flipflop.

| INI | PUT | BEFORE | BEFORE CLOCK                              |      | CLOCK             | MODE OF   |

|-----|-----|--------|-------------------------------------------|------|-------------------|-----------|

| J   | K   | Qn     | Qn      0        1      1        1      1 | Qn+1 | $\overline{Qn+1}$ | OPERATION |

| 0   | 1   | 1      | 0                                         | _    |                   |           |

| 1   | 0   | 0      | 1                                         |      |                   | SET       |

| 1   | 1   |        |                                           | 0    | 1                 | TOGGLE    |

| 0   | 0   | 0      | 1                                         |      |                   |           |

| 1   | 1   | 0      | 1                                         |      |                   |           |

| 0   | 1   | 1      | 0                                         | 4G   |                   |           |

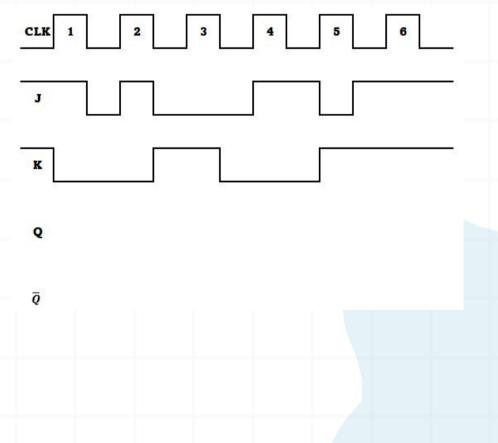

2. Based on figure below, sketch the output Q and  $\overline{Q}$  for gated JK flip-flop with negative edge triggered. (Assume the initial Q=1)

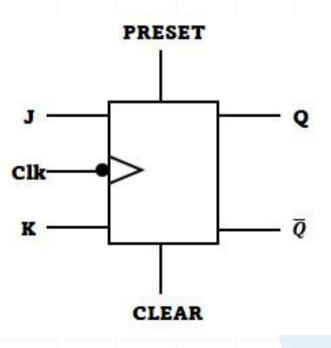

- This flip-flop can also have other inputs called Preset (or SET) and Clear that can be used for setting the flipflop to 1 or resetting it to 0 by applying the appropriate signal to the Preset and Clear inputs.

- These inputs can change the state of the flip-flop regardless of synchronous inputs or the clock.

Logic symbol / Block Diagram

|        | INPUT  |    |        |       |   | PUT |                    |

|--------|--------|----|--------|-------|---|-----|--------------------|

| Asynch | ronous | Sy | nchroi | nous  |   | Q   | MODE OF OPERATION  |

| Preset | Clear  | J  | к      | Clock | Q | Ŷ   |                    |

| 0      | 0      | x  | x      | x     | 1 | 1   | INVALID (INV)      |

| 0      | 1      | x  | x      | x     | 1 | 0   | ASYNCHRONOUS SET   |

| 1      | 0      | x  | x      | x     | 0 | 1   | ASYNCHRONOUS RESET |

| 1      | 1      | 0  | 0      | 1     | Q | Q   | HOLD (H)           |

| 1      | 1      | 0  | 1      | 1     | 0 | 1   | RESET (R)          |

| 1      | 1      | 1  | 0      | 1     | 1 | 0   | SET (S)            |

| 1      | 1      | 1  | 1      | 1     | Q | Q   | TOGGLE (T)         |

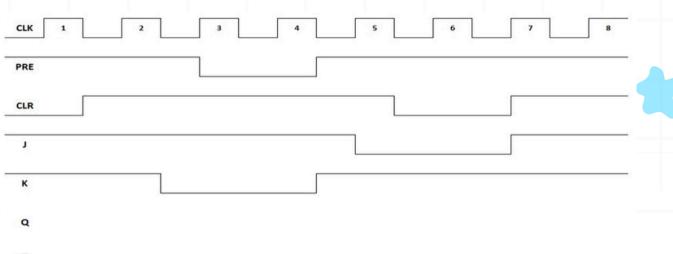

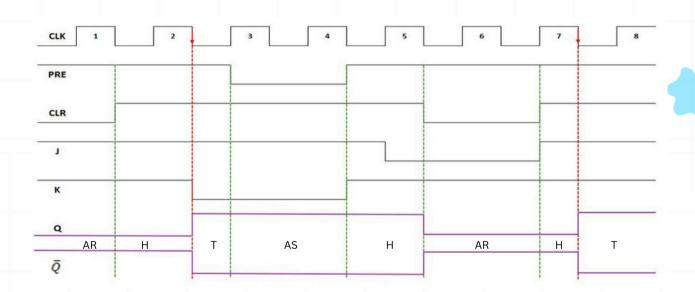

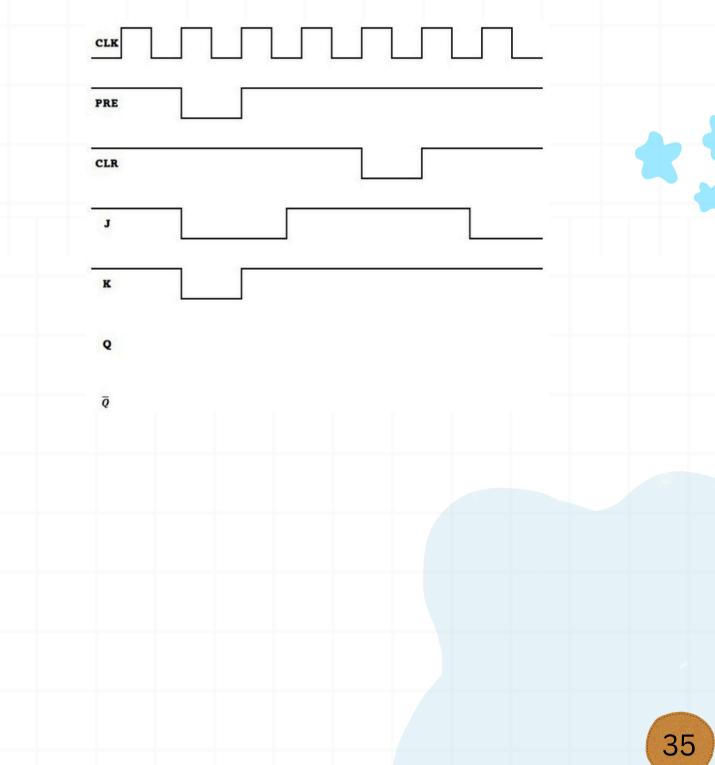

**Example 6** Draw the output Q and Q waveform for negative edge trigger JK flip-flop with Preset and Clear. Initial Q is HIGH.

$\bar{Q}$

1. By using a suitable diagram, explain the operation of the JK flip-flop with Preset (PR) and Clear (CLR).

2. The input for CLK, J, K, PRESET (PRE) and CLEAR (CLR) are shown in figure below. Express the output waveform for Q and  $\overline{Q}$  if the flip-flop is a negative edge triggered and Q initial = 0.

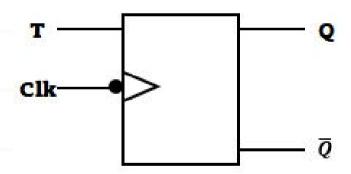

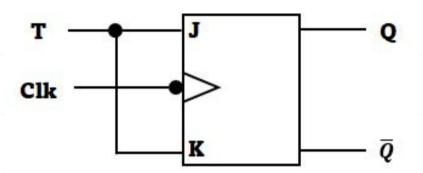

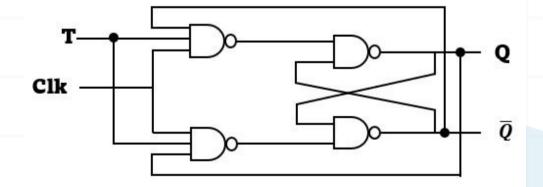

# 3.2 APPLY JK FLIP-FLOPS TO CONSTRUCT T FLIP-FLOP AND D FLIP-FLOP

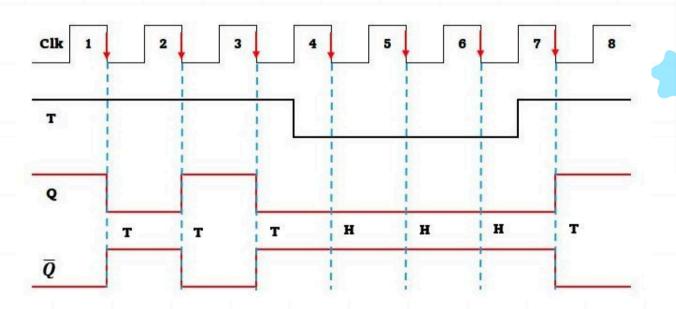

- Only have 1 input, T (Toggle), clock and output.

- Implementation from a JK flip-flop.

Symbol

### Block Diagram

Logic Circuit

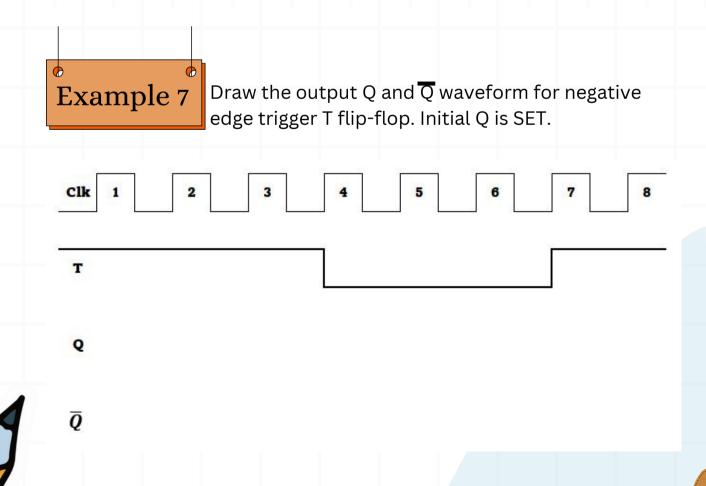

| MODE OF    | OUTPUT |   | INPUT |     |

|------------|--------|---|-------|-----|

| OPERATION  | Q      | Q | т     | CLK |

| HOLD (H)   | Q      | Q | 0     | 1   |

| TOGGLE (T) | Q      | Q | 1     | 1   |

| HOLD (H)   | Q      | Q | х     | 0   |

#### 1. State the output for T flip-flop as given in table below.

| Input | Before | Clock           | After Clock |                   |

|-------|--------|-----------------|-------------|-------------------|

| Т     | Qn     | $\overline{Qn}$ | Qn+1        | $\overline{Qn+1}$ |

| 1     | 1      | 0               |             |                   |

| 0     | 0      | 1               | 0           | 1                 |

| 1     | 0      |                 | 1           | 0                 |

| 1     | 1      | 0               |             |                   |

| 0     |        | 1               | 0           | 1                 |

| 1     | 0      | 1               |             |                   |

2. With the aid of diagram and truth table, explain how T flip-flop can be built by using JK flip-flop.

3(a). Identify the type and built the truth table of flip-flop shown in figure below.

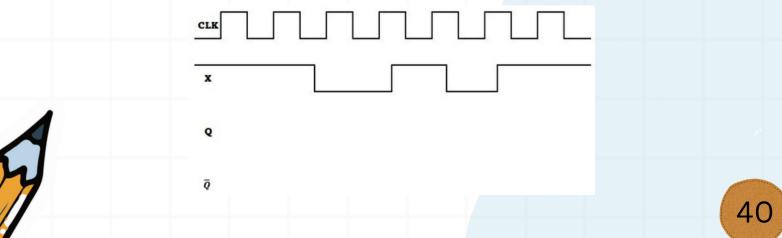

3(b). Sketch the output Q and  $\overline{Q}$  for the flip-flop in 3(a) if the input X is given in figure below. Initial Q is 0 and clock is negative.

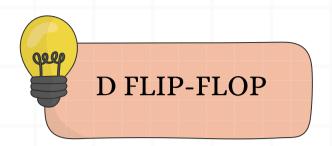

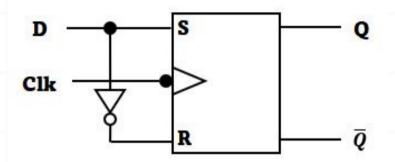

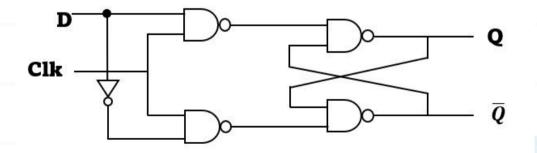

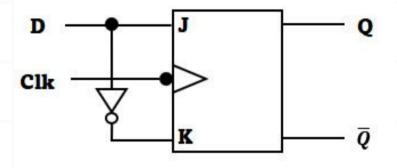

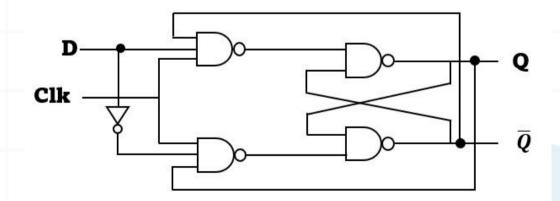

- Only have 1 input, D (Data), clock and output.

- Implementation from a JK and SR flip-flop.

#### Block diagram

Logic Circuit

| MODE OF   | PUT | OUT | UT | INP |

|-----------|-----|-----|----|-----|

| OPERATION | Q   | Q   | D  | CLK |

| RESET (R) | 1   | 0   | 0  | 1   |

| SET (S)   | 0   | 1   | 1  | 1   |

| HOLD (H)  | Q   | Q   | х  | 0   |

43

#### Block diagram

Logic Circuit

| MODE OF   | PUT | OUT | UT | INP |

|-----------|-----|-----|----|-----|

| OPERATION | Q   | Q   | D  | CLK |

| RESET (R) | 1   | 0   | 0  | 1   |

| SET (S)   | 0   | 1   | 1  | 1   |

| HOLD (H)  | Q   | Q   | x  | 0   |

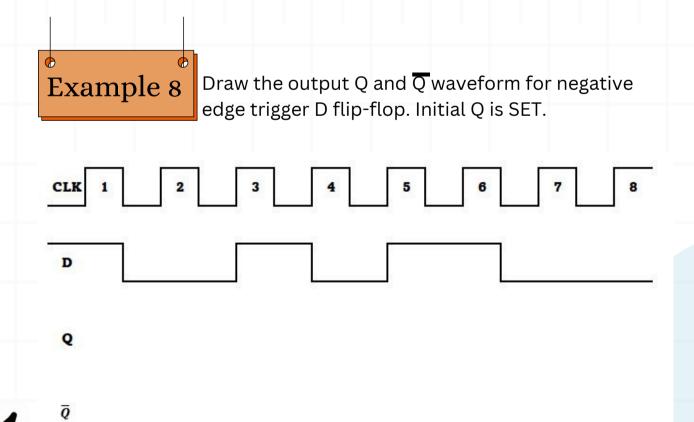

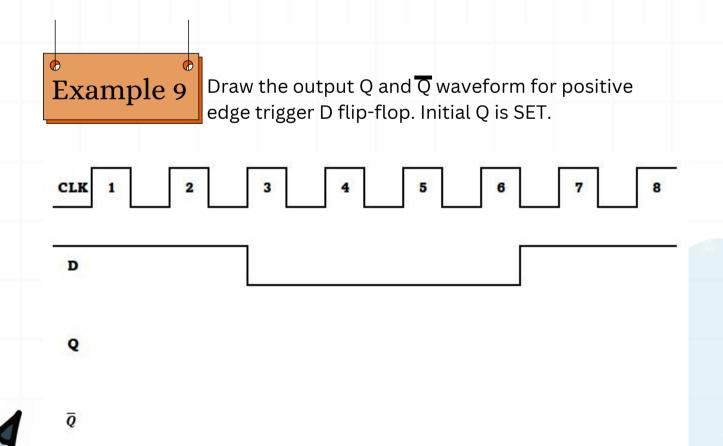

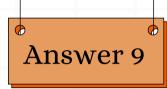

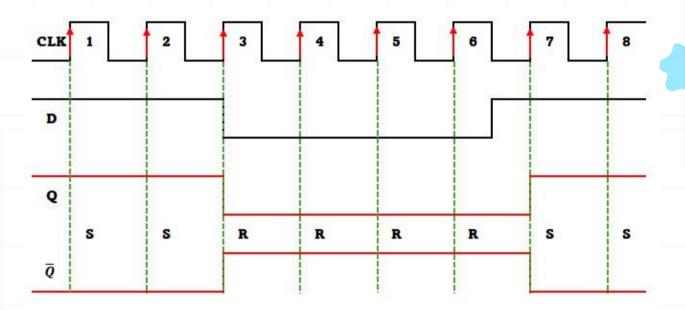

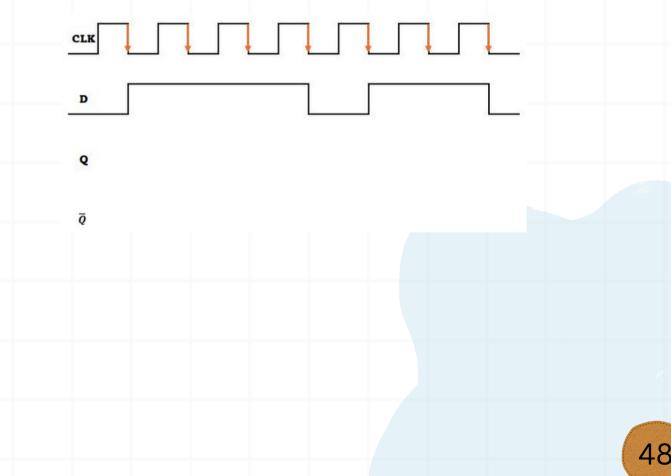

1. Draw the output Q and  $\overline{Q}$  for timing diagram in figure below. Assuming the initial Q=1.

2. With the aid of a diagram and truth table, explain how D flip-flop can be built by using SR flip-flop.

3. Draw the output Q and  $\overline{Q}$  for D flip-flop in figure below. Assume Q initial is 0.

## REFERENCES

- Roger Tokheim, Patrick E. Hoppe (2022). Digital Electronics: Principles and Applications (Ninth Edition). McGraw Hill LLC USA.

- Dr. Sanjay Sharma (2022). Digital Electronics and Logic Design (4th edition). S.K. Kataria & Sons.

- Dr. B.R. Gupta, V. Singhal (2021). Digital Electronics (5th edition).

S.K. Kataria & Sons.

- Dhanasekharan Natarajan (2021). Fundamentals of Digital Electronics. Springer Nature Switzerland.

- Neal S. Widmer, Gregory L. Moss, Ronald J. Tocci (2017). Digital Systems-Principles and Applications (12th ed.). Pearson Higher Ed USA.

- Floyd, L. Thomas (2014). Digital Fundamentals (11th ed.). Pearson Education International.

#### POLITEKNIK UNGKU OMAR

Jabatan Kejuruteraan Elektrik Politeknik Ungku Omar Jalan Raja Musa Mahadi 31400 Ipoh, Perak Tel: 1-300-88-1969 / 05-5457622 Faks: 605-5471162 Laman web: http://www.puo.edu.my

e ISBN 978-629-7635-63-7